# Power Analysis of an Approximate adders under various interpolation factors for DSP Applications

# G. Naveen Balaji, D.Rajesh, S. Sowmya, M. Subashini, P. Suryaprabha

*Abstract*— Energy-efficiency is a critical concern for many systems, ranging from the Internet of things objects and mobile devices to high-performance computers. Moreover, after 40 years of prosperity, Moore's law is starting to show its economic and technical limits. Many circuits are noticed that they are over-engineered and many are error-resilient applications or require less precision than offered by the existing hardware, approximate computing has emerged as a potential solution to pursue improvements of digital circuits. In this regard, a technique to systematically tradeoff accuracy in exchange for an area, power, and delay savings in digital circuits is proposed.

Index Terms—Approximate Adders, CMOS, Low Power, Pass Transistor

#### I. INTRODUCTION

Improving energy efficiency of modern computing systems is the main challenge in today's digital design. Computing capabilities of mobile devices such as smartphones has grown exponentially in the past decades. Additionally, the number of Internet of things devices is expected to reach 21 billion by 2020. The latter not only requires to operate for several years without user intervention, but will also produce a gigantic amount of data that will have to be processed in data centers which are extremely power hungry and need complex cooling systems.

In the past four decades, technology scaling has been leading integrated circuits' advancement. Unfortunately, the growing complexity of deeply scaled technology combined with increasing process-voltage–temperature variations and the poor scaling of Vth, Moore's law is starting to show its limits. Nonetheless, approximate computing which can be applied through different abstraction layers ranging from technology, hardware design, up to algorithm or software level is a potential solution to pursue the challenge of computing advancement and overcome the physical and economical limitations encountered with technology scaling.

Approximate computing has become a promising technique to reduce the power, area and delay constraints in VLSI design, albeit at the expense of a loss in computational accuracy. This technique is applicable to error-tolerant applications such as multimedia, mining and recognition. Generally, there are two methodologies for reducing accuracy by approximation. The first methodology uses a voltage-over-scaling (VOS) technique for CMOS circuits to save power, while also introducing errors into the circuit. The second methodology is based on redesigning a logic circuit into an approximate version.

The main objective of the "Low Power Approximate Adders For General Computing Using Differential Transmission Gate" is to noticing that many circuits are over-engineered and that many applications are error-resilient or require less precision than offered by the existing hardware, approximate computing has emerged as a potential solution to pursue improvements of digital circuits.

#### II. EXISTING SYSTEM

Approximate computing allows remarkable power and energy savings by relaxing computation accuracy while achieving an acceptable processing quality. The key observation is that many applications, such as digital signal processing and neuromorphic systems, have inherent error resilience and hence 100% precision in computation is not required. Particularly, the core of many DSP and neuromorphic10 applications lies in processing specific kernel functions. For example, spiking neural networks heavily perform the leaky integrate-and-fire (LIF) operation to mimic neuron behaviour. Obviously, adders are one primary component for building these arithmetic kernel functions. In addition, comparators are indispensable to determine firing activities in the LIF operation of digital neurons. To this end, it is particularly attractive to design approximate arithmetic units for considerable energy saving in neuromorphic computing.

The approximate adder of leverages a limited number of less significant input bits for carry speculation to increase the overall speed. The critical drawback of this approach is the use of a considerable number of carry generators, which gives rise to large area and high power dissipation. The error tolerant adder I and the lower part OR adder are split into an accurate part for higher output bits and an inaccurate part, which utilizes a modified XOR or an OR function to approximately compute the remaining lower bits.

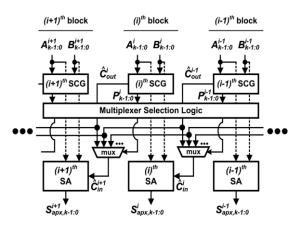

#### A. Approximate Adder - Mux Selection Logic

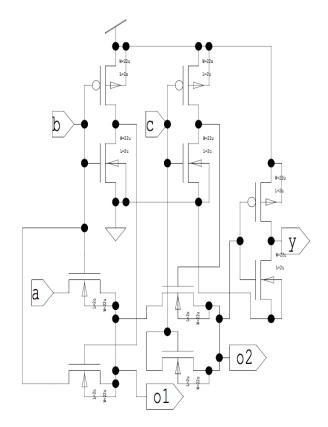

The block diagram of the existing approximate n-bit adder, which is divided into several k-bit sized blocks. Each block contains a k-bit SA and a k-bit sub-carry generator (SCG), which create a partial summation and partial carry-out signal, respectively.

G. Naveen Balaji, Assistant Professor, Department of Electronics and Communication Engineering, SNS College of Technology, Coimbatore, India

**D. Rajesh, S. Sowmya, M. Subashini, P. Suryaprabha**, UG Student Department of Electronics and Communication Engineering, SNS College of Technology, Coimbatore, India

Fig.1 Approximate Adder Using Mux Selection Logic

Note that the SAs can be implemented by any accurate adders, such as ripple-carry adder (RCA) and carry-look ahead adder (CLA). At the beginning of an addition operation, all the SCGs simultaneously create the partial carry-out signals (..., Ci+1, Ci, Ci-1, ...) using only their k-bit inputs.

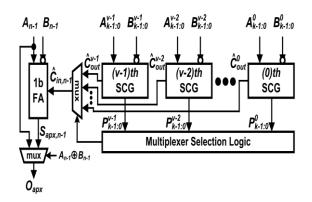

## B. Approximate Comparator - Mux Selection Logic

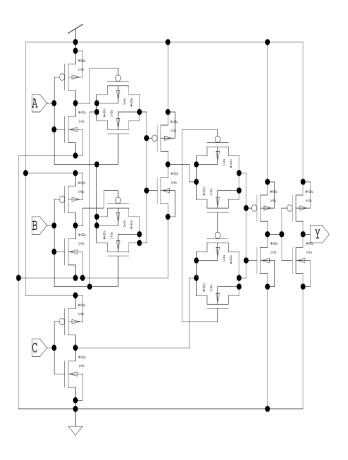

Fig.2 Approximate Comparator Using Mux Selection Logic

This block diagram of the proposed approximate comparator. The n-bit comparator consists of a 1-bit full adder (FA) and v  $(\geq 2)$  k-bit SCGs that are identical to the ones in the proposed adder. It is worth noting that the proposed approximate comparator exploits only kv + 1 MSBs of the n-bit inputs, resulting in area and power reductions. Importantly, the input B is inverted to achieve subtraction operation. Since implementing two's complement necessitates an additional increment or, we employ one's complement to further reduce area and energy with sacrificing an error rate, but still achieving a very low error rate. The FA generates the sign bit Sapx,n-1 (MSB output) of the subtraction between the two inputs by leveraging the speculated carry-in signal Cin,n-1 and the MSB of the two inputs. The speculated carry-in signal is obtained in the same parallel way by the v SCGs and multiplexer selection logic.

The carry prediction is incorrect if all the propagate signals of more than v consecutive blocks are true and a carry is generated in the preceding block, making a carry chain of a length greater than kv. Assuming that the adder inputs A and B are bitwise independent, then the propagate and generate signals are bitwise independent as well.

When the two inputs have the different signs (i.e., An−1 ⊕ Bn-1 = 1), the comparison result is readily obtained by the input MSB without the FA. Therefore, the output multiplexer selects the MSB of the input An-1 if the signs of two inputs are different from each other, otherwise, it chooses the FA output  $S_{apx}$ , n-1. The comparator fails when the signs of the inputs are the same and the carry prediction for the FA is incorrect. The carry speculation is incorrect when all the propagate signals in the v SCGs used for carry prediction are true and a carry generated from the n - kv - 1 least significant bits (LSBs). It is important to note that, we should consider all the propagate signals of the n-kv-1LSBsare true since the proposed comparator adopts one's complement, instead of two's complement, for the subtraction. We assume that the inputs A and B are bitwise independent. Then, the event of the carry prediction error for the FA is given by

$$E_{\rm cin}^{i} = P_{k-1:0}^{i-1} P_{k-1:0}^{i-2} \cdots P_{k-1:0}^{i-v} G_{k-1:0}^{i-v-1}.$$

(1)

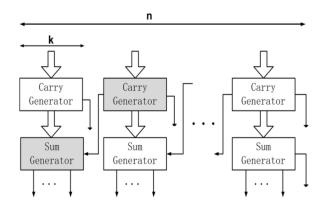

#### C. Approximate Comparator

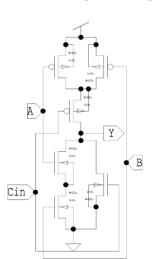

Fig.3 Approximate Comparator Using Combinational Logic

A dynamic segmentation and error compensation scheme is presented in for an approximate adder design. This approximate adder consists of several sub-adders of different sizes divided from an n-bit adder; each of the sub- adders operates in parallel and has a truncated carry input. For convenience, but with no loss in correctness, sub-adders of equal size are considered in this manuscript. More over the error compensation part is neglected because the focus of this manuscript is on analyzing the approximate operation.

The existing comparator fails when the signs of the inputs are the same and the carry prediction for the FA is incorrect. The carry speculation is incorrect when all the propagate signals in the v SCGs used for carry prediction are true and a carry generated from the n - kv - 1 least significant bits (LSBs). It is important to note that, we should consider all the propagate signals of the n-kv-1LSBs are true since the proposed comparator adopts one's complement, instead of two's complement, for the subtraction. We assume that the inputs *A* and *B* are bitwise independent. Then, the event of the carry prediction error for the FA is given by

$$E_{\mathrm{cin},n-1} = P_{k-1:0}^{\nu-1} P_{k-1:0}^{\nu-2} \cdots P_{k-1:0}^{0} (G_{n-k\nu-2:0} + P_{n-k\nu-2:0}).$$

(2)

A. Approximate Adders Using Pass Transistor Logic

## III. PROPOSED SYSTEM

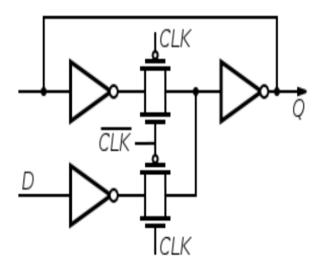

## Pass Transistor Logic

Pass transistor logic (PTL) describes several logic families used in the design of integrated circuits. It reduces the count of transistors used to make different logic gates, by eliminating redundant transistors. Transistors are used as switches to pass logic levels between nodes of a circuit, instead of as switches connected directly to supply voltages. This reduces the number of active devices, but has the disadvantage that the difference of the voltage between high and low logic levels decreases at each stage.

Each transistor in series is less saturated at its output than at its input. If several devices are chained in series in a logic path, a conventionally constructed gate may be required to restore the signal voltage to the full value. By contrast, conventional CMOS logic switches transistors so the output connects to one of the power supply rails, so logic voltage levels in a sequential chain do not decrease. Simulation of circuits may be required to ensure adequate performance.

Fig.4 Complementary Pass Transistor

Complementary pass transistor logic or "Differential pass transistor logic" refers to a logic family which is designed for certain advantage. It is common to use this logic family for multiplexers and latches. CPL uses series transistors to select between possible inverted output values of the logic, the output of which drives an inverter The CMOS transmission gates consist of nMOS and pMOS transistor connected in parallel.

## **Transmission Gate**

Just like transistor, a faucet is connected to a source, the faucet drains in a sink, and the flow of water through the faucet is controlled by a gate (the knob). If the faucet knob (gate) is turned ON water flows from the source to the sink, otherwise if the faucet knob (gate) is turned OFF no water flows. Using transistors as building blocks, we can build larger circuits that perform interesting (logical) operations.

B. Approximate Adders Using Transmission Gates

## Power Analysis of an Approximate adders under various interpolation factors for DSP Applications

C. Approximate Adders Using CMOS Logic

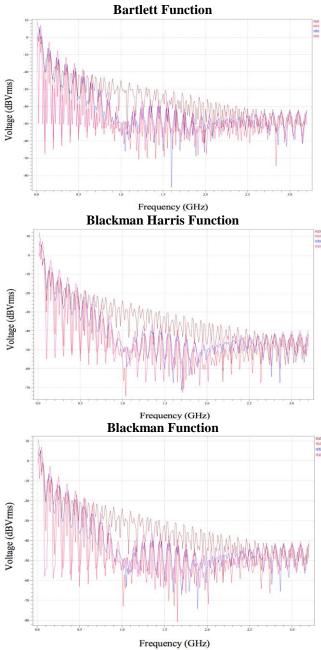

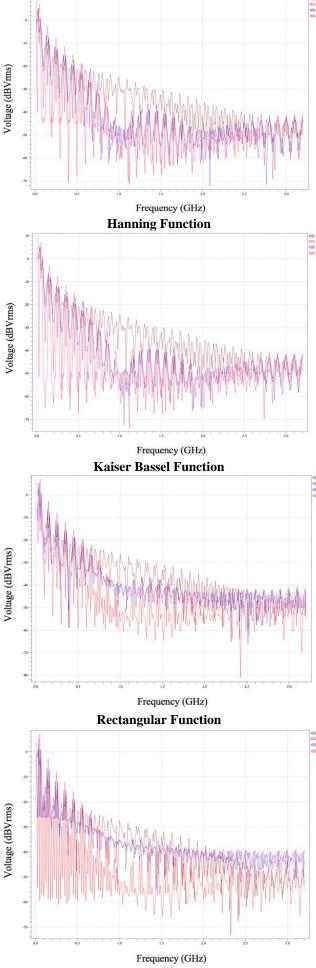

**Hamming Function**

### International Journal of Engineering and Technical Research (IJETR) ISSN: 2321-0869 (O) 2454-4698 (P) Volume-8, Issue-01, January 2018

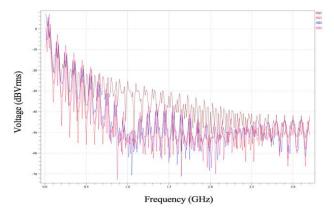

#### Power Results

v1 from time 0 to 8e-008 Average power consumed -> 2.612743e+000 watts Max power 2.794875e-002 at time 7.1e-008 Min power 4.172384e-007 at time 0

### V. CONCLUSION

Approximate adder and comparator designs to considerably reduce energy consumption with a very moderate error rate has been presented for energy efficient neuromorphic VLSI systems. The proposed adder is  $2.4 \times$  faster and 43% more energy efficient over traditional adders and our comparator achieves up to 71% energy saving over the conventional counterparts.

#### REFERENCES

- S. Jankowski, J. Covello, H. Bellini, J. Ritchie, and D. Costa, "The Internet of Things: Making sense of the next mega-trend," Goldman Sachs, 2014.

- [2] K. V. Palem, "Energy aware computing through probabilistic switching: A study of limits," IEEE Trans. Comput., vol. 54, no. 9, pp. 1123–1137, Sep. 2005.

- [3] Low Power Consumption Ternary Full Adder Based on CNTFET

- [4] S. Cheemalavagu, P. Korkmaz, K. V. Palem, B. E. Akgul, and L. N. Chakrapani, "A probabilistic CMOS switch and its realization by exploiting noise," in Proc. IFIP Int. Conf. VLSI, Oct. 2005, pp. 535–541.

- [5] P. Korkmaz, B. E. S. Akgul, K. V. Palem, and L. N. Chakrapani, "Advocating

- [6] Noise as an agent for ultra-low energy computing: Prob- abilistic complementary metal-oxide-semiconductor devices and their characteristics," Jpn. J. Appl. Phys., vol. 45, no. 4B, p. 3307, 2006.

- [7] G. Karakonstantis and K. Roy, "Voltage over-scaling: A cross-layer design perspective for energy efficient systems," in Proc. 20th Eur. Conf. Circuit Theory Design (ECCTD), Aug. 2011, pp. 548–551.

- [8] J. George, B. Marr, B. E. S. Akgul, and K. V. Palem, "Probabilis- tic arithmetic

- [9] and energy efficient embedded signal processing," in Proc. Int. Conf. Compil., Archit. Synth. Embedded Syst., Ser. (CASES), New York, NY, USA, Oct. 2006, pp. 158–168. [Online]. Available: http://doi.acm.org/10.1145/1176760.1176781

- [10] D. Ernst et al., "Razor: A low-power pipeline based on circuit- level timing speculation," in Proc. 36th Annu. IEEE/ACM Int. Symp. Microarchitecture (MICRO), Dec. 2003, pp. 7–18.

[11] P. K. Krause and I. Polian, "Adaptive voltage over-scaling for resilient

- [11] P. K. Krause and I. Polian, "Adaptive voltage over-scaling for resilient applications," in Proc. Design, Autom. Test Europe Conf. Exhibit. (DATE), Mar. 2011, pp. 1–6.

- [12] S. Ghosh, S. Bhunia, and K. Roy, "CRISTA: A new paradigm for low- power, variation-tolerant, and adaptive circuit synthesis using critical path isolation," IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst., vol. 26, no. 11, pp. 1947– 1956, Nov. 2007.

- [13] G.Naveen Balaji, V.Aathira, K. Ambhikavathi, S. Geethiga, R. Havin "Combinational Circuits Using Transmission Gate Logic for Power Optimization" International Research Journal of Engineering and Technology, Vol. 3, Issue 5 (May 2016) pp: 649-654, ISSN: 2395 -0056

- [14] R. ArunSekar, G. Naveen Balaji, A. Gautami, B. Sivasankari "High Efficient Carry Skip Adder in various Multiplier Structures" Advances in Natural and Applied Sciences (Annexure II), Vol. 10 Issue 14 (Special) (Oct 2016) pp: 193-197, ISSN: 1995-0772

- [15] M. Srinivasaperumal, K. Boopathi Raja, G. Naveen Balaji, E. Christina Dally "Concurrent Node Recovery From Failure In Wireless Sensor-Actor Networks" KARI Research Journal, Vol. 1 Issue 4 (Oct - Dec 2016) pp: 28-33, ISSN: 2456-6136

- [16] G. Naveen Balaji, V. Narayanan, V.S. Nivash "Low Power and High performance JK Flip – Flop using 45 nm Technology" International Journal of Engineering

Research in Electronics and Communication Engineering (IJERECE) Vol 3, Issue 10, October 2016, pp:26-29, ISSN: 2394-6849

- [17] M. Srinivasaperumal, K. Boopathi Raja, G. Naveen Balaji, E. Christina Dally "Concurrent Node Recovery From Failure In Wireless Sensor-Actor Networks" Advances in Natural and Applied Sciences (Annexure II), Vol. 10 Issue 17 (Dec 2016) pp: 240-246, ISSN: 1995-0772

- [18] G. Naveen Balaji, R. Prabha, E. Shanthini, J. Jayageetha, Mohand Lagha "Rapid low power Synchronous circuits using transmission gates" Advances in Natural and Applied Sciences (Annexure II), Vol. 10, Issue 17 (Dec 2016) pp: 287-291, ISSN: 1995-0772

- [19] G. Naveen Balaji, S. Chenthur Pandian, D. Rajesh "Fast Test Pattern Generator using ATALANTA M 2.0" Asian Journal of Research in Social Sciences and Humanities (Annexure I) Vol. 7 No. 2 (Feb 2017) pp. 721-729 ISSN: 2249-7315 DOI: 10.5958/2249-7315.2017.00124.1

- [20] G. Naveen Balaji, V. Aathira, K. Ambhikavathi, S. Geethiga, R. Havin "Low Power and High Speed Synchronous Circuits using Transmission Gates" Asian Journal of Research in Social Sciences and Humanities (Annexure I), Vol. 7 No. 2 (Feb 2017) pp. 713-720. ISSN: 2249-7315, DOI: 10.5958/2249-7315.2017.00123.X

- [21] G. Naveen Balaji, S. Anusha, J. Ashwini "GPS Based Smart Navigation for Visually Impaired Using Bluetooth 3.0" Imperial Journal of Interdisciplinary Research (IJIR) Vol. 3, No. 3, 2017, pp. 773-776. ISSN: 2454-1362

- [22] G. Naveen Balaji, D. Rajesh "Smart Vehicle Number Plate Detection System for Different Countries Using an Improved Segmentation Method" Imperial Journal of Interdisciplinary Research (IJIR) Vol. 3, No. 6, 2017, pp. 263-268. ISSN: 2454-1362

- [23] G. Naveen Balaji, N.V. Hari Suriya, S. AnandVikash, R.Arun, S. Arun Kumar "Analysis of Various Liquid Components under Different Temperature and Density Constraints Pertaining To Fractional Distillation" Imperial Journal of Interdisciplinary Research (IJIR) Vol. 3, No. 6, 2017, pp. 664-669. ISSN: 2454-1362

- [24] G. Naveen Balaji, D. Rajesh "Python Based Reverse Timing Algorithm for Human Brain Activity Using Color Psychology" International Journal of Indian Psychology, Vol. 4, No. 3, DIP: 18.01.111/20170403, pp: 79-86, ISSN 2348-5396

- [25] G. Naveen Balaji, S. Chenthur Pandian, D. Rajesh "High Performance Triplex Adder Using CNTFET" International Journal of Trend in Scientific Research and Development, Vol.1, No. 5, pp: 368-373, ISSN 2456 - 6470

- [26] G. Naveen Balaji, S. Chenthur Pandian, S. Giridharan, S. Shobana, J. Gayathri "Dynamic and Non-Linear Charge Transfer Through Opto-Deportation by Photovoltaic Cell" International Journal of Trend in Scientific Research and Development, Vol. 1, No. 5, pp: 486-492, ISSN 2456 - 6470

- [27] G. Naveen Balaji, S. Karthikeyan, M. Merlin Asha "0.18µm CMOS Comparator for High-Speed Applications" International Journal of Trend in Scientific Research and Development, Vol. 1, No. 5, pp: 671-674, ISSN 2456 - 6470

- [28] G. Naveen Balaji, K. Saravanan, R. Poorani, T. Vishnu Priya, R. Reka Raj "Advanced Security System using PIC through Bluetooth" International Journal of Trend in Scientific Research and Development, Vol. 1, No. 5, pp: 675-685, ISSN 2456 - 6470

- [29] G. Naveen Balaji, N.V. Hari Suriya, S. Anand Vikash, S. Arun Kumar, R. Arun, "Gasoline Purity Meter Using Peripheral Interface Controller for Automobile Applications" International Journal of Engineering and Technical Research (JJETR), Vol. 7, No.10, pp:46-55, ISSN: 2321-0869

- [30] G. Naveen Balaji, S.Chenthur Pandian, "Design for Testability of Kipbond Logic" "Perspectivas em Ciência da Informação" (Annexure - I), School of Information Science of the Federal University of Minas Gerais (UFMG), Vol. 22, No. SP.01, pp: 261-284, ISSN 1413-9936