# Optimization of Parallel Computing Algorithm for Shared memory MPSoC

# Kumar Satyam, Arpan Shah, Ramesh Bharti

Abstract— This paper presents design an Dual core processor with the low-power cache memory. In this project, we are present an important area in computer architecture which is a parallel processing in MPSoC. Which Machines using parallel processing is called parallel machines. A parallel machine is executes multiple instructions in one cycle. This type of process works on the SIMD technique in MPSoC The Dual core processor uses new techniques to reduce power consumption and increase the speed relatively single core processor. Since memories are accessed sequentially, it implements a single address bus for read and writes operation.

The support of Simulation on Xilinx, I will compare the different types of parameter such as power consumption, area, delay, of Single core processor and dual core processor. Single core processor is in individual memory of 128 byte and Dual core processor is in shared memory of 128 byte.

Index Terms—MPSoC, ALU, Xilinx, Single and Double Core Processor.

#### I. INTRODUCTION

In today's applications can be handled by future generations of Multi core processor; The MPSoC architectures for Game, internet network processors, high-definition video encoding, multimedia hubs, and base-band telecom circuits, we believe that new applications that will require the development of new MPSoCs will emerge. Implanted computer vision is one example of an emerging field that can use essentially unlimited amounts of computational power but must also happen in real-time, low-power, and low-cost requirements. Multiprocessor systems-on-chips (MPSoCs) are the latest incarnation of the very large scale integration (VLSI) technology. A single integrated circuit/chip can hold over 100 million transistors, logic gates and for the Semiconductors predicts that chips with a billion transistors are within reach. Binding all this raw computing power requires designers to move beyond logic design into computer architecture. real-time deadlines, very low-power operation, and so on. These opportunities and challenges make MPSoC design an important field of research. project, we presented an important area in computer architecture which is a parallel processing in MPSoC. Which Machines employing parallel processing are called parallel machines. A parallel machine performs multiple instructions in one cycle. This type of process works on the SIMD technique in MPSoC. I will discuss on single core processor and dual core processor. On the other hand, by the help of

Simulation on Xilinx, I will compare the different types of parameter such as power consumption, area, delay, of Single core processor and dual core processor. In this paper I will discuss on single core processor and dual core processor. On the other hand I will compare the different types of parameter such as, speed power and area. Suggests the behavioral design method for VHDL implementation of a 32-bit ALU using Xilinx Tool, The Multi-processor operation with Shared Memory combination can effectively improve the performance of this system.

#### II. SINGLE CORE PROCESSOR

The single core processor, it processor work with mainly two parts 1) ALU and 2) RAM. . Single core processor is in individual of 128 byte.

A calculation is identified, examined and implemented using the Xilinx software.128 byte data storage RAM for the this processor.

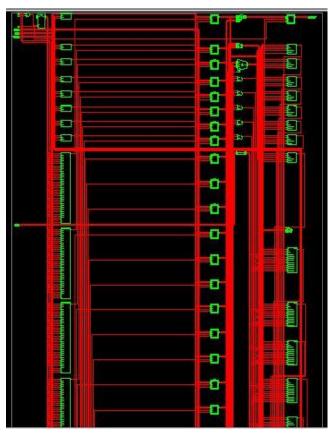

FIGURE 1: RTL SCHEMATIC OF SINGLE CORE PROCESSOR

The figure 1 shows the RTL Schematic of Single core Processor with detailed information having size of 128 bytes with input lines read, write, clock, opcode and address line and output line.

Kumar Satyam, student M.Tech.(VLSI), JaganNath University, Jaipur, India,9024672476.

Arpan Shah, Assistant Professor, Department of ECE, JaganNath University, Jaipur, India,0978259194.

Ramesh Bharti, Associate Professor, Department of ECE, JaganNath University, Jaipur, India.

III. DUAL CORE PROCESSOR

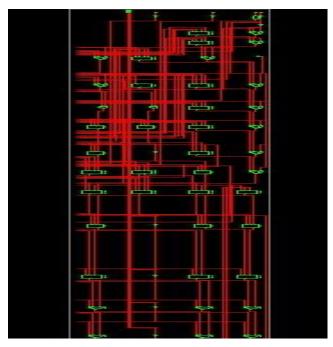

FIGURE 2: RTL SCHEMATIC OF DUAL CORE PROCESSOR

The figure 2 shows the RTL Schematic of Dual core Processor with detailed information having size of 128 bytes with input lines read, write, clock, opcode, reset and address line and output line.

## IV. RESULT

The table shows the comparison between Single Core Processor and Dual Core Processor. The result clearly shows that the power consumption of Dual Core processor is lower than the one Single core Processor. Power is calculated using SPARTAN-3 XPE-11.1, power estimating tool from Xilinx.

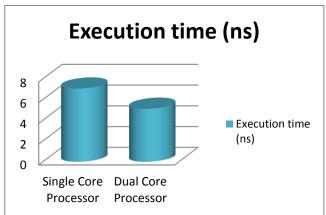

#### A) Execution Time

The performance results of Single Core Processor and Dual-Core Processor generated from Xilinx tool. The total execution time for the processors were as follows: Total Execution time of Single Core Processor is 7.052 seconds Total Execution time of Core Processor is 5.103 seconds Given,

*n= Ex Single* Core *Processor –Ex Dual* Core *Processor/Ey(Dual* Core *Processor)*\* 100

Figure 3: Graph shows comparison of Single Core Processor and Dual core processor in terms of time of execution in (ns)

The above results confirm that Dual-Core Processor is over 3.814 % faster than Single Core Processor.

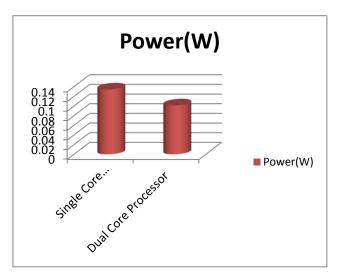

## B) Power Analysis

The power analysis is done with Xilinx power estimator (XPE) that express in a excel sheet The static power of proposed design is same as Single core processor but dynamic power is reduced and total power consumption decreases.

Figure 3: Graph shows comparison of power of Single core processor and Dual core processor in terms of power consumption in (w)

Above diagram is show power analysis both Single core processor and Dual core processor. Both towers are different. Because Single Core Processor is use less no of LUTs). Comparatively Dual core processor. But the dynamic power is reduces. of Dual core processor

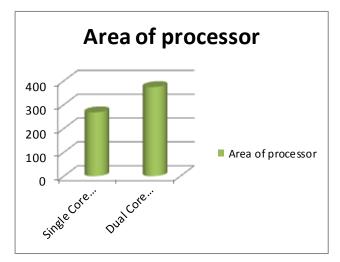

#### B) Area

Area of Processor is depend on the how many LUTs use in the system. LUT stands for a Look Up Table. The many number of Flip Flop is inbuilt it, that's a execute the different type of operation. same as in a single core processor and Dual core processor built a different no. of LUTs.

Figure 6: Graph shows comparison of circuit area of Single core processor and Dual core processor

## International Journal of Engineering and Technical Research (IJETR) ISSN: 2321-0869, Volume-3, Issue-6, June 2015

From the above graphs we can clearly make out that overall power consumption of Dual core processor is reduced than the previous one. The dynamic power consumed by Dual core processor is 32.67 % lesser than the Single core processor.

# V. CONCLUSION

The table shows the comparison between Single core processor and Dual core processor.

Though there is a increase in circuitry in case of Dual core processor due to added LUT, and but the time of execution decreases, still the overall product of delay (ns) and power (W) is reduced, which shows the improvement in result. There is a power reduction of 32.67% in the circuit of Dual core processor

| Name of Device           | Execution<br>Time (ns) | Power (W) | Area<br>(LUT) |

|--------------------------|------------------------|-----------|---------------|

| Single Core<br>Processor | 7.052                  | 0.134     | 268           |

| Dual Core<br>Processor   | 5.103                  | 0.101     | 374           |

Table 2: Comparison of overall power consumption of Dual core processor

#### REFERENCES

- [1] Ramesh S. Goankar, "Microprocessor Architecture, Programming and Applications with 8085", 5thEdition, Prentice Hall

- [2] Parkhurst, J., Darringer, J. & Grundmann, B. 2006, "From Single Core to Multi-Core: Preparing for a new exponential", Computer-Aided Design, 2006. ICCAD '06. IEEE/ACM International Conference on, pp. 67.

- [3] Lance Hammond, Basem A. Nayfeh, Kunle Olukotun, "A Single-Chip Multiprocessor," Computer, vol. 30, no. 9, pp. 79-85, Sept. 2007

- [4] Roy, A., Jingye Xu & Chowdhury, M.H. 2008, "Multi-core processors: A new way forward and challenges", Microelectronics, 2008. ICM 2008. International Conference on, pp. 454.

- [5] Patterson, D. 2010, "The trouble with multi-core", Spectrum, IEEE, vol. 47, no. 7, pp. 28-32, 53.

- [6] Wayne Wolf, Fellow, IEEE, Ahmed Amine Jerraya, and Grant Martin, Senior Member, IEEE "Multiprocessor System-on-Chip (MPSoC) Technology", IEEE Transactions On Computer-Aided Design Of Integrated Circuits And Systems, Vol. 27, No. 10, October 2008 1701,

- [7] Mohit Gambhir, Edward F. Gehringer, and Yan Solihin, "Animations of important concepts in parallel computer architecture," in Proceedings of the 2007 workshop on Computer architecture Education, 2013 IEEE 8th International Conference on Industrial and Information Systems, ICIIS 2013, Aug. 18-20, 2013, Sri Lanka

- [8] L. S. K. Udugama and Janath C Geeganage. "Students' experimental processor: a processor integrated with different types of architectures for educational purposes." in Proceedings of the 2006 workshop on Computer architecture education: held in conjunction with the 33<sup>rd</sup> International Symposium on Computer Architecture (WCAE '06). ACM, New York, NY, USA,. doi: 10.1145/1275620.1275632

- [9] International Journal of Computer Science and Communication Engineering IJCSCE Special issue on "Emerging Trends in Engineering" ICETIE 2012 "VHDL Implementation of 32-Bit Arithmetic Logic Unit (Alu)" Geetanjali 1 and Nishant Tripathi,

- [10] Goodacre, J. & Sloss, A.N. 2005, "Parallelism and the ARM instruction set architecture", Computer, vol. 38, no. 7, pp. 42-50.

- [11] V.Venkatachalam and M. Franz. "Power reduction techniques for microprocessor systems", ACM Computing Surveys, 37(3):195–237, 2005.

- [12] 2012 IEEE 25th Computer Security Foundations Symposium, "Secure Information Flow for Concurrent Programs under Total Store Order" Jeffrey A. Vaughan University of California, Los Angeles Todd Millstein, University of California, Los Angeles,

- [13] IEEE Transactions On Industrial Informatics, Vol. 9, No. 3, August 2013 In NOCS '07: Proc First Int. Symp. Networks-on-Chip, 2007., A. Hansson and K. Goossens, "Trade-offs in the configuration of a network on chip for multiple use-cases,"

- [14] In Proc. 41<sup>st</sup> Annu. Des. Autom. Conf., 2004 "The future of multiprocessor systems-on-chips,", W. Wolf,

- [15] Falcao, G., "How Fast Can Parallel Programming Be Taught to Undergraduate Students?," Potentials, IEEE, vol.32, no.4, pp.28,29, Aug. 2013. doi: 10.1109/MPOT.2012.2234507

- [16] Yousun Ko, Bernd Burgstaller, and Bernhard Scholz, "Parallel from the beginning: the case for multicore programming in the computer science undergraduate curriculum," in Proceedings of the 44th ACM technical symposium on Computer science education (SIGCSE '13), ACM, New York, NY, USA, 415-420. doi:10.1145/2445196.2445320

**Kumar Satyam** student of M.Tech VLSI Technology in JaganNath University, Jaipur. I am about to complete my M.Tech (VLSI) in 2015 from Jagan Nath University. and B.E degree in 2012 from Rajeev Gandhi Technical University I am currently working in VLSI field.

**ARPAN SHAH,** Asst. Prof. Dept. of ECE in JaganNath University, Jaipur. He has completed his M.Tech(VLSI) in 2012 from GyanVihar University and B.E degree in 2008 from Rajasthan University. He is currently working in the VLSI field.

**Ramesh Bharti** Asso. Prof. Dept. of ECE in JaganNath University, Jaipur. He is currently pursuing PhD from JaganNath University. He has completed his M.Tech(E&CE) in 2010 from MNIT Jaipur, and B.E degree in 2004 from Rajasthan University. He is currently working in the wireless communication