# A Survey: To Design Low Noise Digital Decimation Filter for Sigma-Delta-ADC

# Pramod Kumar Singh, Kanika Sharma

*Abstract*— This paper focused on the low noise digital decimation filter design techniques categorized as sigma-delta modulation based on word length. The general purpose DSP applications include classical LMS algorithms reported using sigma-delta modulator A single bit sigma-delta A/D converter with medium oversampling ratio for the processing of audio ,seismic and biomedical signal. A second-order single-stage sigma-delta modulator single bit quantize signal with oversampling ratio 96.Finaly a low noise filter discussed and compare order of modulator and decimation.

*Index Terms*— oversampling, downsampling, quantization noise, noise shaper, decimation filter, CIC compensation filter.

## I. INTRODUCTION

There is no surprises that more task are accomplished in the Digital signal processing(DSP). Filter required large number of accumulator and multiplier in per sampling period. The alternate solution is Field Programmable Gate Arrays (FPGA) for digital filter task. The design for ADC the nyquist rate is  $fs \ge 2^{*}f_{b}$ , where  $f_{b}$  is the high frequency component of the input signal and f<sub>s</sub> is sampling frequency. To insure the filter the signal component about fs/2 to avoid aliasing must have very narrow transition band[1]. The resolution of Nyquist rate conversion is low which is not suitable for every low signal voltage conversion. Oversampled ADC is preferred over nyquist rate due to high SNR (Signal to noise ratio) and high resolution[2].Here sigma delta modulator behave like noise shaper and digital decimation filter and CIC compensator filter are also used to remove band quantization nose ensure much higher SNR.

Some obvious applications that require fast and efficient digital filters are decimation filters, audio filter and software defined radio, so this requires high throughput. To achieve fast, noiseless and efficient implementations, various techniques are proposed. Reducing the complexity of the multiplier is to reduce the word length in both the input and the filter coefficient. This paper also focuses on these methods. To improve the efficiency of the digital filtering operations here many techniques are used in form of Sigma-Delta modulation like.We examine the synthesis and design of such techniques including general purpose short word length (SWL) DSP in this paper. The design focused on the off chip digital decimation filters for single bit sigma-delta

Pramod Kumar Singh, Deptt. Of Eletronices Engg., NITTTR, Chandigarh

A/D converter with medium over sampling ratio. To reduce hardware requires, multiplier less FIR filter architecture are used[3].The anti aliasing filter must have a very narrow transition band which is not easy to realize. Also the resolution of Nyquist rate converter is low which is suitable for a very low voltage converter.thus the reducation in base band quantizing noise is equivalent to increasing the effective resolution of the digital output. It is reduce by using CIC compensation filter design[4].

**Basic of Sigma- Delta modulator-** The simplest predictive modulator is the linear Delta modulator. Most of the in band noise outside signal frequency band that further improvement in the SNR it can be achieved by pushing noise to high frequency. This should be obtain only if signal transfer function is a low pass where as and noise transfer function is high pass[5]. This technique is called noise shaping and can be easily and efficiently implemented by modifying the delta modulator. So the integration of the input signal is encoded rather than the input signal directly[6].

Clearly integration being a linear function does not affect system transfer function. The significant modification of Delta modulation system is called Sigma-Delta Modulator.In FIR filter much work on the design and implementation of the Sigma-Delta modulation in various forms. More recently sigma-delta modulation based bit stream adder and multipliers modules have been described[7,8].To perform the filtering operation full precision filter coefficient where zero padded by R to match the oversampling ratio of the sigma-delta modulator. The Decoder circuit which comprises cascade comb and base band filter where used to remove the quantization noise and aliases from the filter out put signal. However the output signal was in a multi bit format in all of these scheme[9].

Overall and efficient implementation of narrow band digital filter thorough a requantizing operation has shown a 50% reduction in logic resources as compared to traditional FIR filter implementation. Signal encoding with sigma-delta modulation work as an ADC with coder circuit because single bit coder have no longer requirement for a conventional ADC[10].There no interpolation is required in this setup as a signal passing through Sigma-Delta modulator the output of modulator is very high sampling rate. After filtering out high frequency quantization noise, it possible to reduce the sample rate by using decimation filter.

Manuscript received April 12, 2015.

Kanika Sharma , Deptt. Of Eletronices Engg., NITTTR, Chandigarh

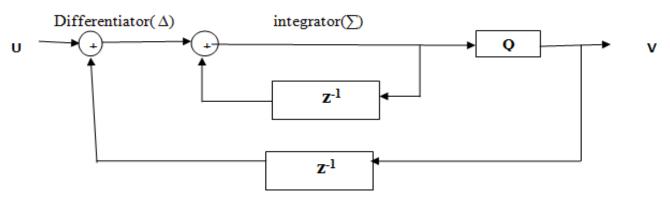

Fig.1. Block Diagram of second order sigma- delta modulator.

## II. CHOICE OF FILTER TOPOLOGY -

Fall on two categories

(a)Remove Shaped Quantization Noise- Best choice of sigma-delta modulator should provide good noise shaping at low OSR.As the OSR increase, the order of filter should be increases to maintain same frequency response when sampling rate is high noise move to high frequency and most of it lies above base band[10,11]. The spectral density of noise at output of the modulator is

N(f)=

$$e\sqrt{2\tau}(2\sin(\pi f\tau))^{1}$$

The spectral density of the decimated noise will be

$$N'(f) = e\sqrt{2}\tau \left(\frac{2\sin(\pi f N\tau)}{N}\right)^{l}$$

When this noise is equalize to compensate for the signal filtering it's become  $N_0'(f) = e\sqrt{2\tau (2\sin(\pi f\tau))^1} (\frac{\sin c(\tau f)}{\sin c(N\tau f)}) = 0 < f < f_0$

Decimation filter attenuating noise at any high frequency noise that accompanies the signal, when it aliases baseband, here loss of resolution will be small. Decimation filter provides least attenuation for this noise. The decimation filter is the overall protection against the out-of-band noise[12]. It was found that using more than two cascaded comb filter did not improve the trade of between signal to noise rate of the coded output and the OSR. .

The decoder for this filter is used to reconstruct the original signal by resampling to the Nyquist rate and removing quantization noise by using low pass filter. The use of cascade comb filter as reported in [3] was adopted to further simplify the decoder design whilst removing any alias introduced into the system from the FIR filter. To perform the filtering operation full precision filter coefficient where zero padded by R to match the oversampling ratio of the sigma-delta modulator. Decoder circuit comprising cascade comb and base band filter where used to remove the quantization noise and aliases from the filter out put signal. However the output signal was in a multi bit format in all of these scheme.

(b)CIC Compensation Filter-The comb filter operation is equivalent to rectangular window finite impulse response filter (FIR). The comb filter must be used more additional digital filter stages. A comb filter of length N is a FIR filter with all N coefficients equal to one. The comb filter transfer function is

$$H(Z) = \frac{Y(Z)}{X(Z)} = \sum_{N=0}^{N-1} Z^{-N}$$

in the discrete time domain for N=4

$$y(n) = x(n) + x(n-1) + x(n-2) + x(n-3)$$

Now from equation (1)

$$H(Z) = 1 + Z^{-1} + \dots + Z^{N-1}$$

$$\frac{Y(Z)}{X(Z)} = \frac{1 - Z^{-N}}{1 - Z^{-1}}$$

$$Y(Z) = X(Z) \left[\frac{1}{1 - Z^{-1}}\right] \left[1 - Z^{-N}\right] \dots (2)$$

$$H(Z) = H_1(Z) Hc(Z) = \frac{Y(Z)}{X(Z)}$$

..... (3)

..... (1)

Where

$$H_1(Z) = \left\lfloor \frac{1}{1 - Z^{-1}} \right\rfloor$$

and

$H_c(Z) = \left[ 1 - Z^{-N} \right] X(Z)$

We generalize equation number (3) for M number of integrator comb filter pairs, and R is the rate change factor. The equivalent time domain impulse response of CIC filter can be viewed as a cascade of M rectangle pulses. Each rectangular pulse has rn taps. Then equation (3) becomes

$$H(Z) = \frac{Y(Z)}{X(Z)} = H_{1}^{M}(Z) * H_{C}^{M}(Z^{R}) ... (4)$$

The CIC filter frequency response does not have a wide and sharp flat pass band. To overcome the magnitude drop, a FIR filter that has a magnitude response that is the inverse of the CIC filter can be applied to achieve frequency response correction filters called compensation filter. Compensation filter used for down convertor follows the CIC filter. This filter always operates at the lower rate in a rate conversion design.Now, since the comb filter will be followed by an decimator, the differentiation function can be done at the lower rate.

Highly symmetric structure of a CIC filter allows efficient in

## International Journal of Engineering and Technical Research (IJETR) ISSN: 2321-0869, Volume-3, Issue-4, April 2015

hardware but its pass band is not flat. This problem can be alleviated by a compensation filter. The method for designing CIC compensating filters sample rate conversion system. The MATLAB signal processing Toolbox is used to design the cofficents of the compensation FIR filters. The magnitude response of an N-stage CIC filter at high frequency( $f_s$ ).

for large number of stage ,the CIC filter frequency response does not have a flat,wide pass band.to Overcome the amplitude droop,a filter that has aamplitude response which is the inverse of the CIC filter and can be applied to achieve frequency response correction is called a CIC compensation filters.To achieve a more efficient hardware solution the compensation filter operates at the lower in a rate conversion design.Amplitude response of the compensation filter is the inverse of CIC is[4,13].

$$|H_{C}(f)| = |MR \frac{\sin (f\pi/R)}{\sin(\pi Mf)}| = |\frac{\pi Mf}{\sin(\pi Mf)}|^{N} = |\operatorname{sinc}^{-1}(Mf)|^{N}$$

.....(6)

The H(f) of the casecade CIC and compensatation filter are

$H(f) = H_1(f).H_C(f)$  ....(7)

That is more time sharing in the compensation FIR filter to achieve a flat pas band, the compensation FIR filter should have a magnitude response is the inverse of CIC FIR filter. When R is large the compensation filter response can be approximated by the inverse sinc function, so the compensation filters sometimes to as the 'inverse sinc' filter. If R is change the compensation filter are also a multi-rate filters. Also in CIC and compensation demonstrate of choosing pass band width on noise amplification in the stop band. Choice of pass band width is important when desiging the CIC filter and compensation filter cascade. The pass band edge to be less than a quarter of the null on the low frequency scale. The solution of filter stage is multiple decimation stages, and it is decimated by 4 and CIC filter is followed by a compensation FIR filter that imppinted additional decimation by-2[4,14].

#### III. SUMMARY

In this survey work on efficient low noise filter design by employinSigma-Delta modulator. A single bit signal processing technique are used is known as SWL[15]. In synthesized hardware efficient and single bit FIR filters. The work provides an important analysis of the relation between oversampling ratio, signat-to-noise ratio, resister size(bit), order of decimation filter and modulator. Noise and buffering problem is reduces in concept of paper and using CIC compensation filter[4,13].

#### **REFERENCE-**

- S. R. Norsworthy, R. Schreier, and G. C. Temes, Delta-Sigma Data Converters: Theory, Design, and Simulation. Piscataway, NJ: IEEE Press, pp. 381, 1997.

- [2]Geerts, Y., Steyaert, M.S.J., Sansen, W.M.: A 3.3-V, 15-bit Delta-Sigma ADC with a Signal Bandwidth of 1.1 MHz for ADSL Applications. IEEE J. Solid-State Circuits 34, Vol. 7,927–936, 1999.

- [3] Subir Kr. Maity, Himadri Sekhar Das "FPGA Based Hardware Efficient Digital Decimation Filter for Sigma Delta ADC" International Journal of Soft Computing and Engineering(IJSCE), Vol-1, Issue-6, Jan 2012.

- [4] Understanding CIC Compensation Filters, Application Note 455 http://www.altera.com/literature/an/an455.pdf.

- [5] T. D. Memon, P. Beckett, and Z. M. Hussain, "Analysis and design of a ternary FIR filter using sigma delta modulation," in Proceedings of the IEEE 13th International Multitopic Conference (INMIC '09), pp. 476–480, December 2009.

- [6] P. W. Wong, "Fully sigma-delta modulation encoded FIR filters," IEEE Transactions on Signal Processing, vol. 40, no. 6, pp. 1605–1610, 1992.

- [7] C. L. Chen and A. N. Willson, "Higher order Σ-Δ modulation encoding for design of multiplierless FIR filters," Electronics Letters, vol. 34, no. 24, pp. 2298–2300, 1998.

- [8] J. C. Candy, "Decimation for sigma delta modulation," IEEE Transactions on Communications, vol. 34, no. 1, pp. 72–76, 1986.

- [9] S. Kershaw, et al., "Realisation and Implementation of a Sigma-Delta Bitstream FIR filter," IEE Proceedings—Circuits, Devices and Systems, vol. 143, pp. 267–273, 1996.

- [10] Sangil Park, Principles of Sigma Delta Modulation for Analog to Digital Converters .Motorola Digital Signal Processors.

- [11] A. C. Thompson, Z. M. Hussain, and P. O'Shea, "A single-bit narrow-band bandpass digital filter,"Australian Journal of Electrical and Electronics Engineering, vol. 2, no. 1, pp. 31–40, 2005.

- [12]Vishal Awasthi, Krishna Raj,"Application of Hardware Efficient CIC Compensation Filter in Narrow Band Filtering,"World Academy of Science, Engineering and Technology International Journal of Electrical, Computer, Electronics and Communication Engineering Vol:8, No:9, 2014.

- [13] Vishal Awasthi, Krishna Raj," A New Approach to Design an Efficient CIC Decimator Using Signed Digit Arithmetic,"World Academy of Science, Engineering and Technology International Journal of Electrical, Computer, Electronics and Communication Engineering Vol:7, No:11, 2013

- [14] C. Dick and F. Harris, "High-Performance FPGA Filters using Sigma-Delta Modulation Encoding," in Proceedings of the IEEE International Conferences on Acoustics, Speech, and Signal Processing (ICASSP '99), pp. 2123–2126, 1999.

- [15]Mohammed Arifuddin Sohel, K. Chenna Kesava Reddy, Syed Abdul Sattar, "Design of Low Power Sigma Delta ADC" International Journal of VLSI design & Communication Systems (VLSICS) Vol.3, No.4, August 2012.

# Author name:

pramod kumar singh, student, M.ENITTTR, Chandigarh